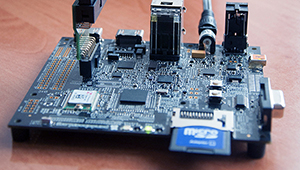

Układy reprogramowalne FPGA

Stanowimy doświadczoną, elastyczną grupę ekspertów w zakresie projektowania i uruchamiania układów (aplikacji) cyfrowych w oparciu o technologię układów reprogramowalnych FPGA/CPLD. Dysponujemy szeroką wiedzą i ogromnym doświadczeniem w zakresie optymalizacji projektów dla układów reprogramowalnych.

Zakres usług:

- projektowanie i realizacja projektu układu cyfrowego dla platformy FPGA/CPLD

- tworzenie elementów bibliotecznych / podzespołów (IP Core – Intellectual Property Core) i wdrożenie ich w aplikacji klienta

- tworzenie modeli symulacyjnych (behawioralnych), środowisk symulacyjnych (testbench) i usługi w zakresie symulacji i testowania systemów cyfrowych

- optymalizacja i dopasowanie istniejących projektów dla wybranych technologii

- optymalizacja timingów i zajętości zasobów docelowego układu reprogramowalnego

- adaptacja i integracja zakupionych bloków funkcjonalnych (IP-Core) do aplikacji klienta

- tworzenie i integracja sprzętowo-programowa systemów On-Chip (SoC)

- doradztwo w zakresie wyboru układu FPGA/CPLD

- tworzenie skryptów w Tcl/Tl, integracja aplikacji DesignFlow na potrzeby projektu klienta

- przebudowa istniejących projektów na potrzeby użycia najnowszej technologii

- dokumentowanie systemów i istniejących projektów

Technologie

- Nasza firma dysponuje zespołem inżynierów posiadającym rozległą wiedzę, kompetencje i doświadczenie w zakresie następujących technologii.

- znajomość dostępnych na rynku architektur układów reprogramowalnych firm ALTERA, Xilinx, Actel / Microsemi, Lattice.

- do realizacji projektów wykorzystujemy język VHDL

- implementacja układów w narzędziach syntezy/implementacji: Altera Quartus, Xilinx Foundation/ISE/WebPack, Synplify, Actel Libero, Lattice Diamond, LeonardoSpectrum, etc.

- symulacja układów cyfrowych w środowiskach : Aldec Active-HDL, ModelSim

- mamy doświadczenie w implementacji układów o wysokiej częstotliwości pracy do 200 MHz

- doświadczenie w obróbce dużej ilości danych w czasie rzeczywistym, transmisji i obróbki danych szeregowych oraz równoległych

- doświadczenie z dużymi projektami VHDL w liczbie bramek systemowych 1 mln.